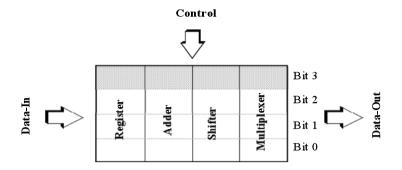

#### **Bit-Sliced Design**

### Topic 9 Arithmetic Circuits & Datapaths

Peter Cheung Department of Electrical & Electronic Engineering Imperial College London

> URL: www.ee.ic.ac.uk/pcheung/ E-mail: p.cheung@ic.ac.uk

#### Tile identical processing elements

| Nov-22-10 | E4.20 Digital IC Design | © Prentice Hall | Topic 9-1 | Nov-22-10 | E4.20 Digital IC Design | © Prentice Hall | Topic 9 - 2 |

|-----------|-------------------------|-----------------|-----------|-----------|-------------------------|-----------------|-------------|

|           |                         |                 |           |           |                         |                 |             |

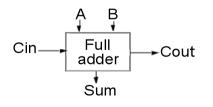

# **Full-Adder**

| АВ         |   |   |                              |   |    |                 |

|------------|---|---|------------------------------|---|----|-----------------|

|            | A | В | <i>C</i> <sub><i>i</i></sub> | S | Co | Carry<br>status |

| adder Coul | 0 | 0 | 0                            | 0 | 0  | delete          |

| Sum        | 0 | 0 | 1                            | 1 | 0  | delete          |

|            | 0 | 1 | 0                            | 1 | 0  | propagate       |

|            | 0 | 1 | 1                            | 0 | 1  | propagate       |

|            | 1 | 0 | 0                            | 1 | 0  | propagate       |

|            | 1 | 0 | 1                            | 0 | 1  | propagate       |

|            | 1 | 1 | 0                            | 0 | 1  | generate        |

|            | 1 | 1 | 1                            | 1 | 1  | generate        |

|            |   |   |                              |   |    |                 |

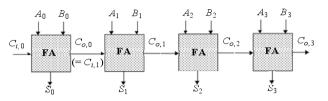

### **The Binary Adder**

Topic 9-3

Nov-22-10

## **The Ripple-Carry Adder**

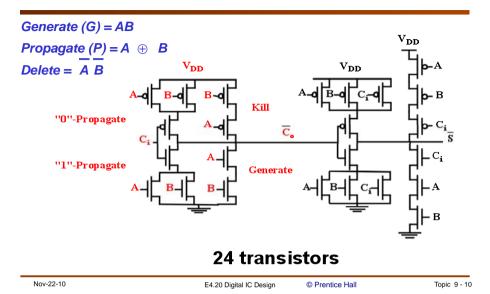

Define 3 new variable which ONLY depend on A, B

Generate (G) = AB

Propagate (P) =  $A \oplus B$

Delete = A B

$$C_o(G, P) = G + PC_i$$

$$S(G, P) = P \oplus C_i$$

| Can also derive expressions for | S and $C_o$ based on D |

|---------------------------------|------------------------|

| and P                           |                        |

| Nov-22-10 | E4.20 Digital IC Design | © Prentice Hall | Topic 9-5 |

|-----------|-------------------------|-----------------|-----------|

|           |                         |                 |           |

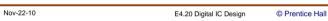

Worst case delay linear with the number of bits  $t_{\text{d}} = O(N)$

$$t_{adder} \approx (N-1) t_{carry} + t_{sum}$$

Goal: Make the fastest possible carry path circuit

E4.20 Digital IC Design © Prentice Hall

Topic 9 - 6

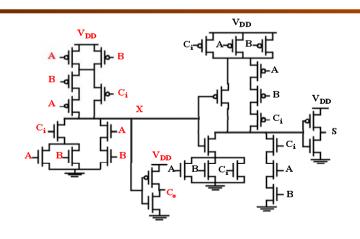

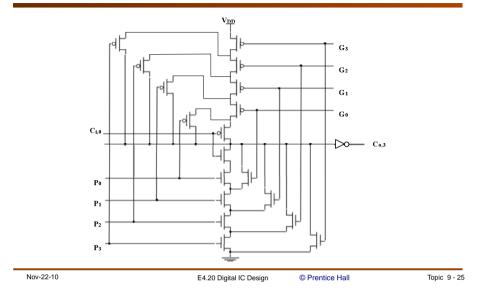

#### **Complimentary Static CMOS Full Adder**

### **28 Transistors**

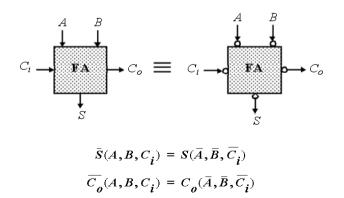

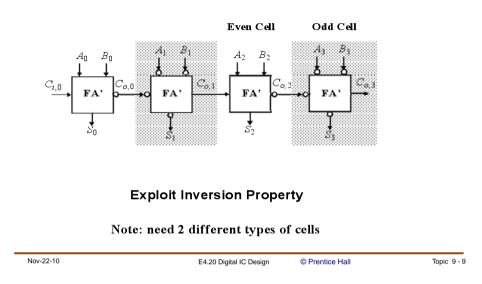

# **Inversion Property**

#### Minimize Critical Path by Reducing Inverting Stages

#### The better structure: the Mirror Adder

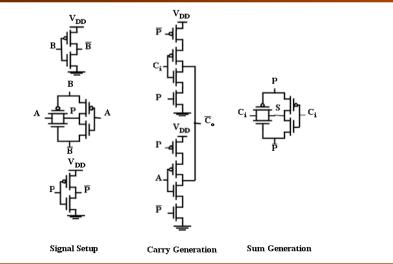

# **The Mirror Adder**

- •The NMOS and PMOS chains are completely symmetrical. This guarantees identical rising and falling transitions if the NMOS and PMOS devices are properly sized. A maximum of two series transistors can be observed in the carry-generation circuitry.

- •When laying out the cell, the most critical issue is the minimization of the capacitance at node  $C_0$ . The reduction of the diffusion capacitances is particularly important.

- •The capacitance at node  $C_o$  is composed of four diffusion capacitances, two internal gate capacitances, and six gate capacitances in the connecting adder cell.

- •The transistors connected to C<sub>i</sub> are placed closest to the output.

- •Only the transistors in the carry stage have to be optimized for optimal speed. All transistors in the sum stage can be minimal size.

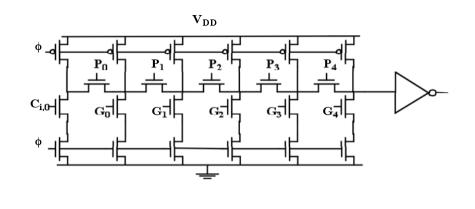

#### **Quasi-Clocked Adder**

Topic 9 - 11

Nov-22-10

### **Manchester Carry Chain**

| Nov-22-10 | E4.20 Digital IC Design | © Prentice Hall | Topic 9 - 13 |

|-----------|-------------------------|-----------------|--------------|

|           |                         |                 |              |

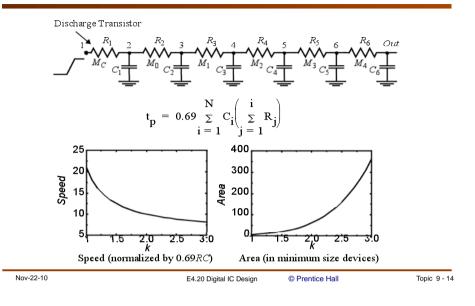

#### **Sizing Manchester Carry Chain**

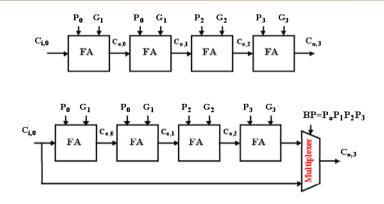

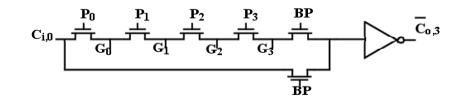

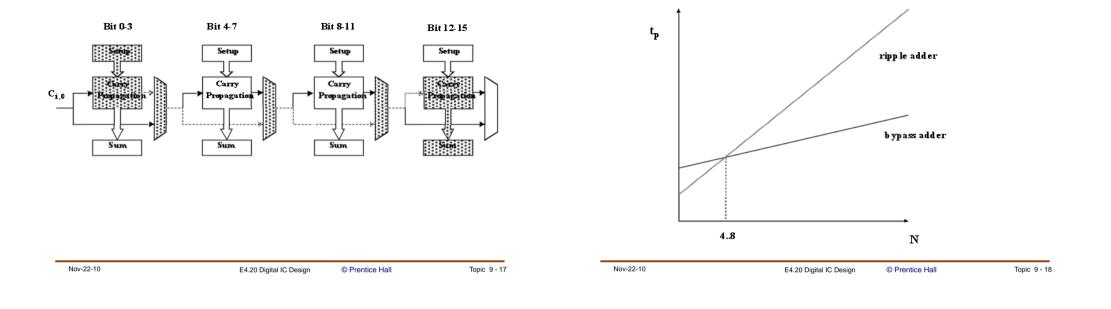

# **Carry-Bypass Adder**

Idea: If (P0 and P1 and P2 and P3 = 1) then  $C_{o3} = C_0$ , else "kill" or "generate".

#### **Manchester-Carry Implementation**

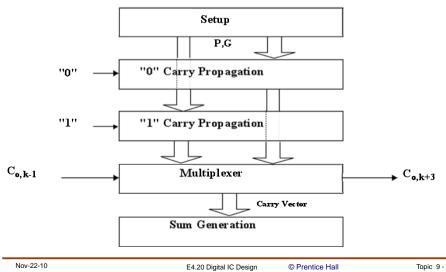

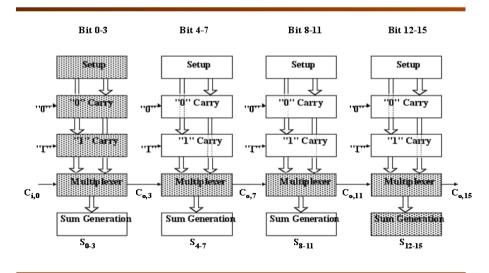

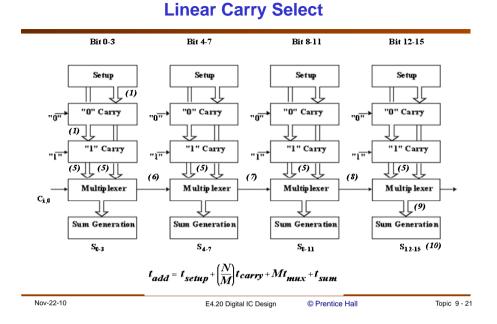

# **Carry-Select Adder**

**Carry-Bypass Adder (cont.)**

### **Carry Select Adder: Critical Path**

**Carry Ripple versus Carry Bypass**

© Prentice Hall

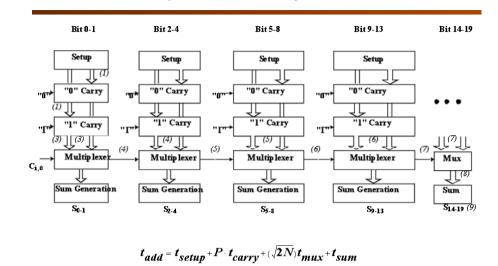

#### **Square Root Carry Select**

Topic 9 - 22

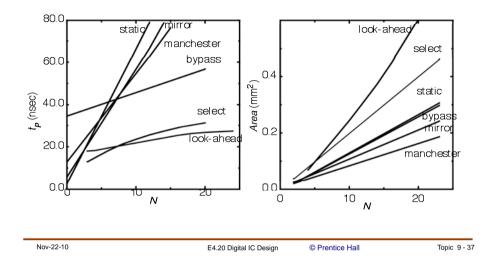

### **Adder Delays - Comparison**

Topic 9 - 23

#### LookAhead - Basic Idea

# Look-Ahead: Topology

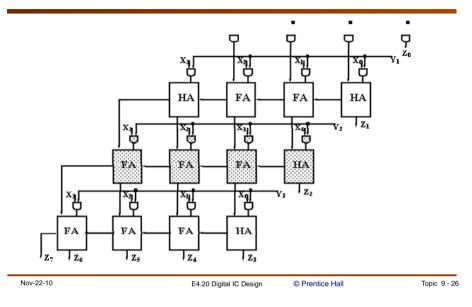

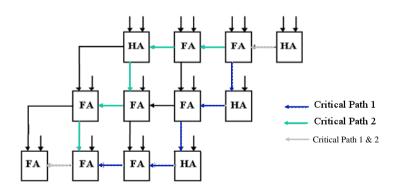

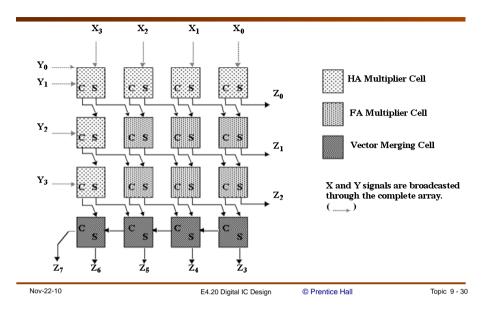

## **The Array Multiplier**

#### The MxN Array Multiplier — Critical Path

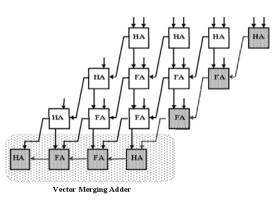

### **Carry-Save Multiplier**

$t_{mult} = (N-1)t_{carry} + (N-1)t_{and} + t_{merge}$

#### **Multiplier Floorplan**

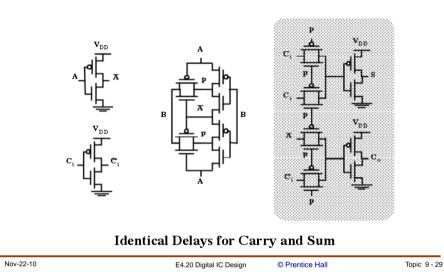

# Adder Cells in Array Multiplier

**Multipliers** —Summary

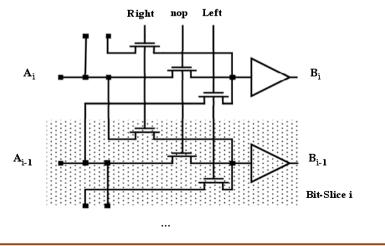

**The Binary Shifter**

- Optimization Goals Different Vs Binary Adder

- Once Again: Identify Critical Path

- Other possible techniques

- Logarithmic versus Linear (Wallace Tree Mult)

- Data encoding (Booth)

- Pipelining

### FIRST GLIMPSE AT SYSTEM LEVEL OPTIMIZATION

Topic 9 - 31

Nov-22-10

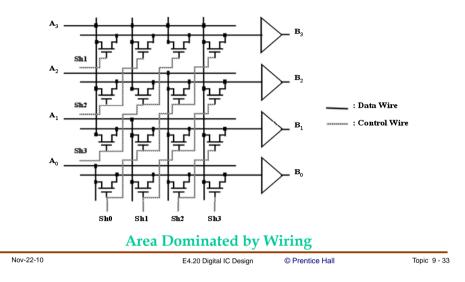

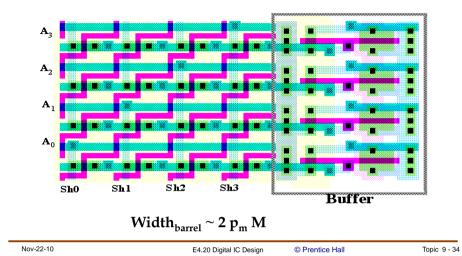

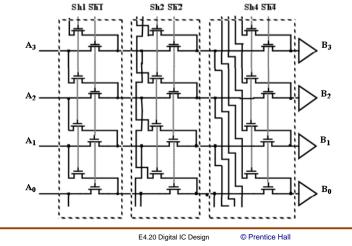

#### **The Barrel Shifter**

4x4 barrel shifter

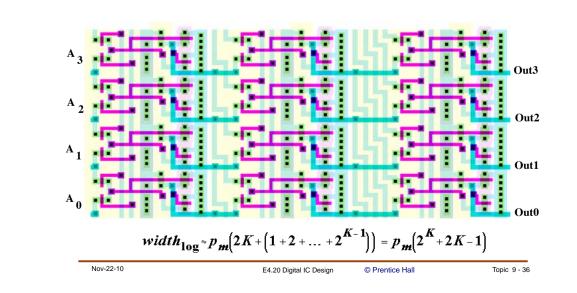

**Logarithmic Shifter**

Topic 9 - 35

### Design as a Trade-Off

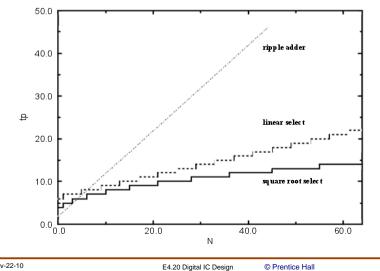

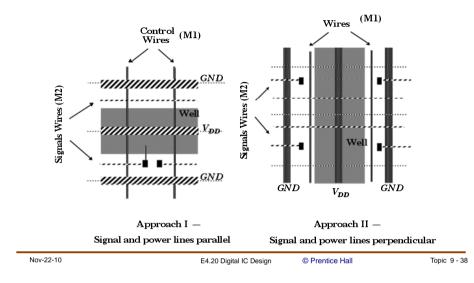

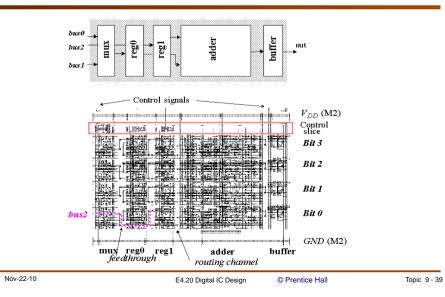

## Layout Strategies for Bit-Sliced Datapaths

### Layout of Bit-sliced Datapaths

### Layout of Bit-sliced Datapaths

| <ul> <li>(a) Datapath without feedthroughs</li></ul>             | (b) Adding feedthroughs       | (c) Equalizing the cell height reduc |

|------------------------------------------------------------------|-------------------------------|--------------------------------------|

| and without pitch matching <li>(area = 4.2 mm<sup>2</sup>).</li> | (area = 3.2 mm <sup>2</sup> ) | the area to 2.2 mm <sup>2</sup> .    |

|                                                                  |                               |                                      |

E4.20 Digital IC Design © Prentice Hall